Conventional memory technologies like SRAM and DRAM face different limitations in nanoscale technologies such as high leakage current and low density.

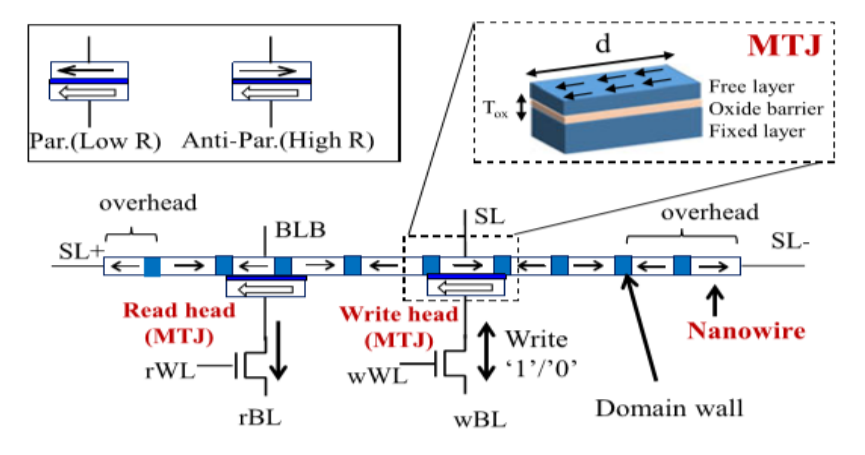

This has resulted in introducing emerging Non-Volatile Memory (NVM) technologies. Domain-Wall Memory (DWM) is an NVM that has the highest density among all NVMs. The read and write performance of DWM is comparable to STT-MRAM. As a result, DWM is suitable for use in cache memory. Besides all the good features, DWM faces some reliability challenges. These challenges are even more important when DWM is used for cache memory because cache memory has the highest read and write rate in the memory hierarchy. A conventional solution for reliability enhancement is employing Error-Correcting Codes (ECCs).

In this research, we use cache compression for making more space available for stronger ECCs with less hardware overhead. This method reduces the uncorrectable error rate by 60.12 percent, on average. The hardware and latency overheads of this method are negligible.

Key Words:

DWM-based Caches, Domain-Wall Memory, Reliability, Error Correction Codes, Cache Compression

Latest Posts

-

Dec 06, 2024

-

Oct 25, 2024