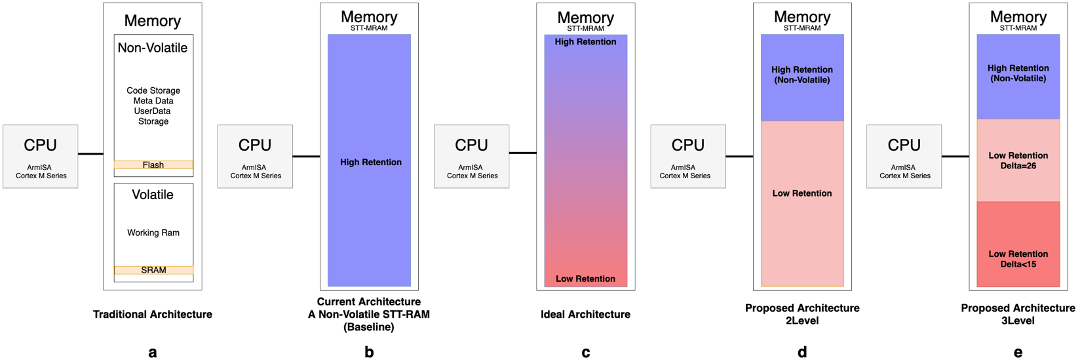

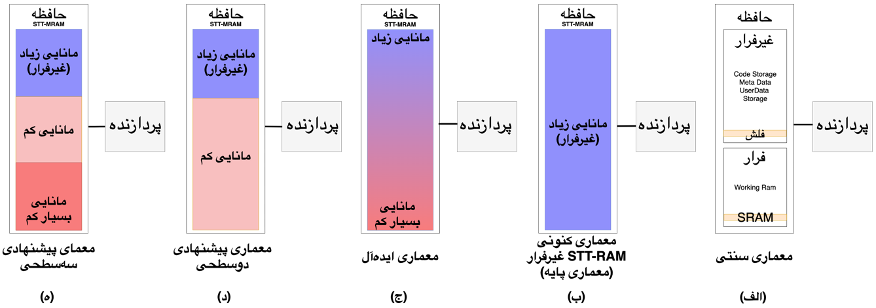

Nowadays, devices connected to the Internet of Things (IoT) are widely used in human life. Since these devices generally provide power from an independent energy source such as batteries or by extracting energy from the outer environment, it is essential to improve the power consumption in these devices. Memory is used in many systems, including devices connected to the IoT, to store program codes and data. Therefore, reducing energy in the memory of these devices will reduce the average energy consumption. In IoT applications, different data are written with different patterns in memory. Some data are written in short- time intervals, and others are written only once for a long time. The same action with the different write requests causes a waste of energy. STT-RAM is a promising memory for replacing SRAM and Flash in IoT devices. However, its high write energy is a drawback. Previous studies tried to use the non-volatility relaxation for CPU cache, but it is needed to use it in main memory and IoT devices. In this work, we propose a multi-retention level STT-RAM for IoT main memory. First we propose a two-level retention memory architecture. Then we investigate the effect of more relaxed retention levels on energy consumption. To the best of our knowledge, this is the first study that does a thorough investigation for finding the proper ∆ for STT-RAM in IoT applications. This architecture needs a proper data mapping. We then propose a static memory mapping for using the suggested memory architecture. Our two-level memory architecture reduces the energy consumption by up to %71 as the best case and by an average of %63, compared to conventional non-volatile STT-RAM.

Latest Posts

-

Dec 06, 2024

-

Oct 25, 2024